栏目分类

4nm分辨率!全新晶体管3D成像技术来袭:可轻松发现内部缺陷

发布日期:2024-08-11 20:28 点击次数:80

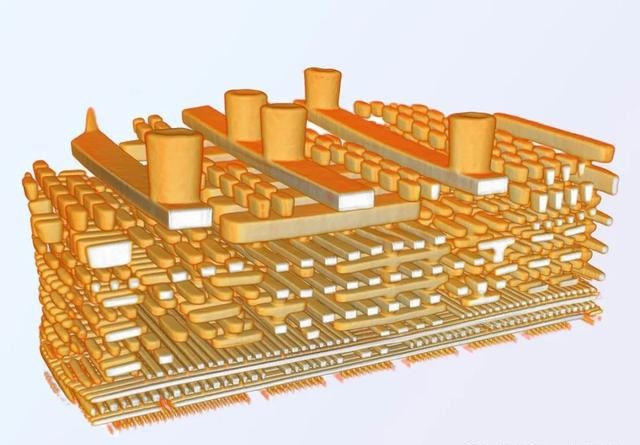

8月5日消息,近日瑞士保罗·谢勒研究院的一组科学家,包括Tomas Aidukas和Mirko Holler,与瑞士苏黎世联邦理工学院的Gabriel Aeppli和美国南加州大学的Tony Levi一起开发出了改进的X射线成像技术,被称之为 ptychographic X 射线层析成像 (PyXL)技术,分辨率高达4nm,可以在不破坏芯片的前提下,提供芯片内部晶体管及布线的清晰的3D图像,以揭示芯片内部的设计/制造缺陷。

Levi说,他们希望提供一种替代方案,以替代用于执行芯片质量控制和揭示芯片设计的耗时、破坏性的过程。

使用最先进的芯片成像技术,“你真的需要提前知道你在寻找什么,”位于美国俄勒冈州希尔斯伯勒的英特尔铸造厂的首席工程师Bao hua Niu说,他没有参与这项研究。他说,今天的芯片非常复杂,仅靠电气测试无法确定缺陷的位置。工程师混合使用光学成像和其他方法来发现潜在问题区域。然后,他们用扫描电子显微镜对芯片表面的那部分进行成像,最后用透射电子显微镜(TEM)取一片芯片进行进一步成像。当他们发现缺陷时,他们可以返回并纠正他们的设计。整个过程非常的复杂,并且耗时耗力。

而PyXL这种新的成像技术,是使用在称为同步加速器的粒子加速器上产生的高能X射线。这些光束可以完全穿透芯片,无需切片。“与光学显微镜不同,制作镜头非常困难,”Levi谈到X射线范围时说。他的团队已经成功通过用相干的高能X射线束从不同角度反复照亮样品,芯片中的微小特征会衍射光线。然后,算法根据衍射 X 射线的强度和相位重建最可能的图像版本。这种成像通常称为层析成像。

“你可以看到他们是如何精确地放置金属层的,有了这个分辨率,你可以看到晶体管的组装情况以及它们使用的材料。”Levi说,这种成像技术的初始版本PyXL提供了大约19nm的分辨率,足以辨别芯片内部的互连,但由于太粗糙,依然无法对单个晶体管的特征进行辨别。为了进一步提升分辨率,该团队试图消除一个主要的噪声源,即可能使图像模糊的微小振动。

幸运的是,他们找到了解决方案,即连拍图像,然后使用计算方法来分类它们。Levi说:“我们拍摄多张短时照片,将它们堆叠在一起,并消除抖动以获得稳定的衍射图案。这使得他们在《自然》杂志上报道的分辨率达到 4nm。Levi 认为该团队有一条达到 1nm 分辨率的途径。

英特尔的Niu表示,这种X射线计算机断层扫描技术的分辨率比TEM提供的分辨率还要好4到5倍。但这种权衡是值得的,因为该技术不需要切割和破坏芯片,并且可以提供更深的3D图像:工程师可以看到芯片的整个5μm 深度,而不是在TEM下可见的10到30nm深度。

Niu 在英特尔的团队实施了新流程,并致力于提高芯片产量和性能。他说,新方法应该使工程师更容易、更快地找到芯片缺陷。制造过程并不总能实现设计师所追求的功能,成像可以帮助工程师将设计与现实更紧密地结合在一起。“这就是你的设计目的,这是根据你的设计实际制作的东西,“他说。“它给你提供了物理验证。”

Levi的团队使用这种方法对使用台积电的7nm 节点工艺制造的AMD Ryzen 5处理器进行了成像。结果包括其FinFET晶体管的结构和特性的详细信息。Levi说,这些图像可能非常具有启发性。“你可以看到他们是如何精确地放置金属的。有了这个分辨率,你可以看到晶体管的组装情况以及它们使用的材料。X射线图像还可以揭示互连网络,即连接芯片上晶体管的金属线。“事物的连接方式告诉你芯片是如何工作的,”他说

“你可以弄清楚芯片的设计工程和制造到底有多好。你可以看到一个芯片的质量。“Levi说。

Niu说,随着晶体管和芯片获得更多的3D特征,获得更高分辨率的3D视图变得越来越重要。晶体管变得越来越小,不再是平面的——FinFET 和即将推出的栅极全能晶体管都从表面突出或分层。包括英特尔在内的半导体制造商正计划在未来几代中将芯片的电源互连从芯片的正面移至背面,这增加了额外的复杂性。

“计量学是半导体制造继续进步的关键,”Niu说。PyXL技术“是一项非常好的研究工作,可以满足关键需求。因为你如果无法衡量,你就无法改进。”

编辑:芯智讯-浪客剑